AI摘要:本文分析了运算放大器(运放)的稳定性,通过OPA364的开环增益曲线,探讨了运放的等效电路。文章详细讨论了运放的输入阻抗、输出阻抗以及闭环增益,并提供了相应的仿真结果。通过测量负载电压,验证了运放等效电路的准确性。最后,文章展示了在不同频率下的闭环增益,证实了仿真结果与实际测量数据的一致性。

Powered by AISummary.

运算放大器稳定性分析——运放等效电路

开环增益等效电路

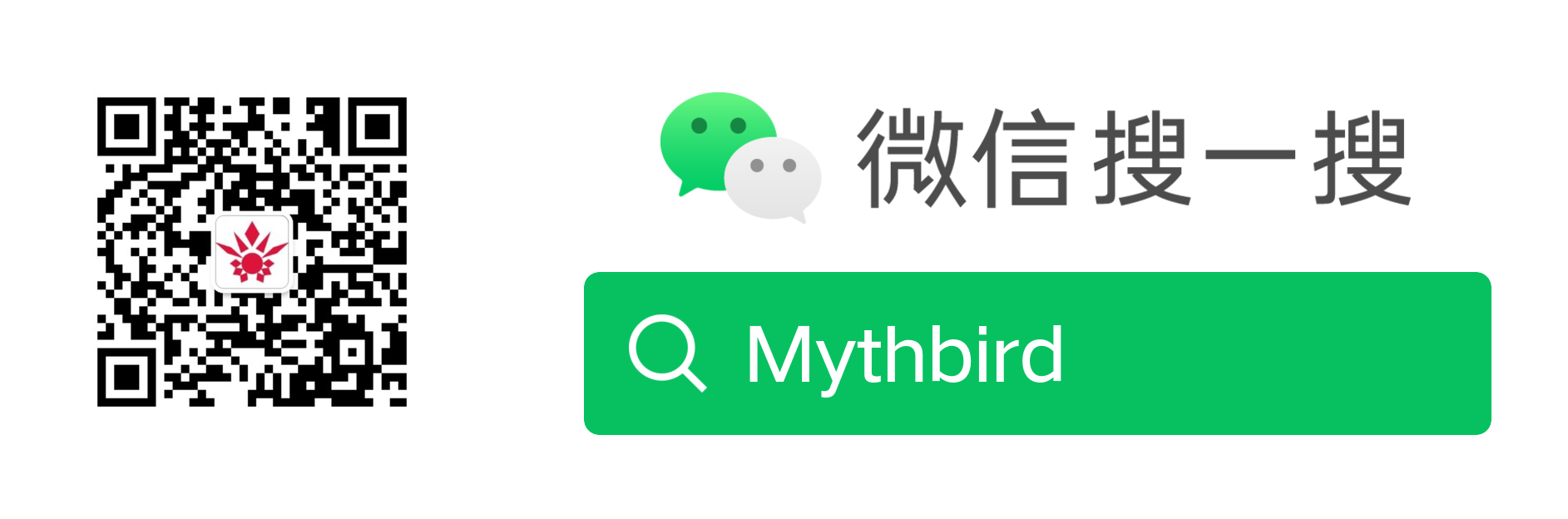

由于运放内部由寄生电容,导致运放的相位并不是一直不变的,而是根据频率变化的。OPA364的开环增益如下图所示。

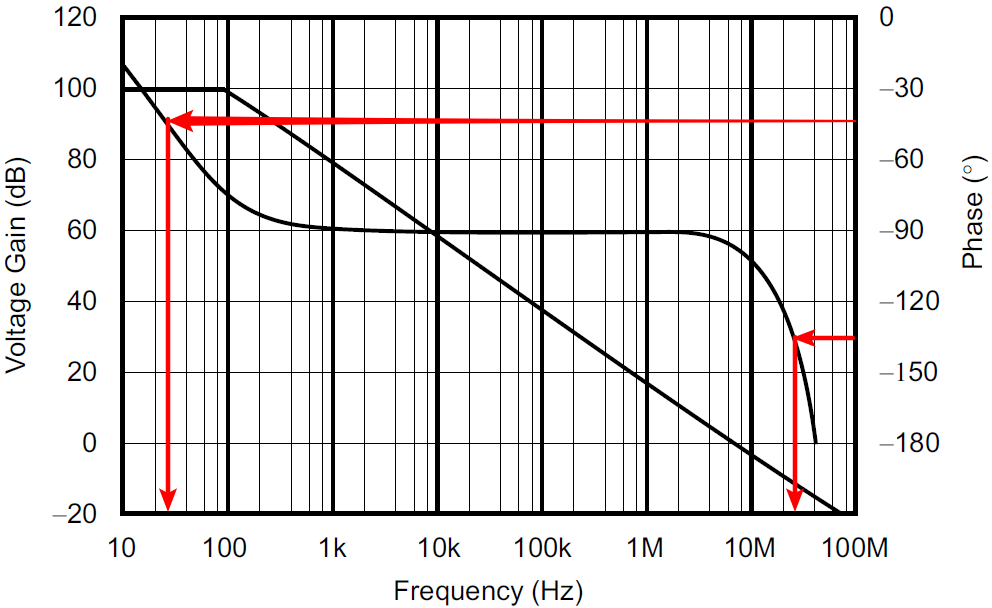

低频极点为25Hz,高频极点为25MHz。使用RC模拟极点,VCVS(压控电压源)隔离。等效电路如下图所示。

可见与Datasheet基本符合,但是在高频80MHz附近不完美,当然可以继续取180°的极点进行优化。这里不在赘述。

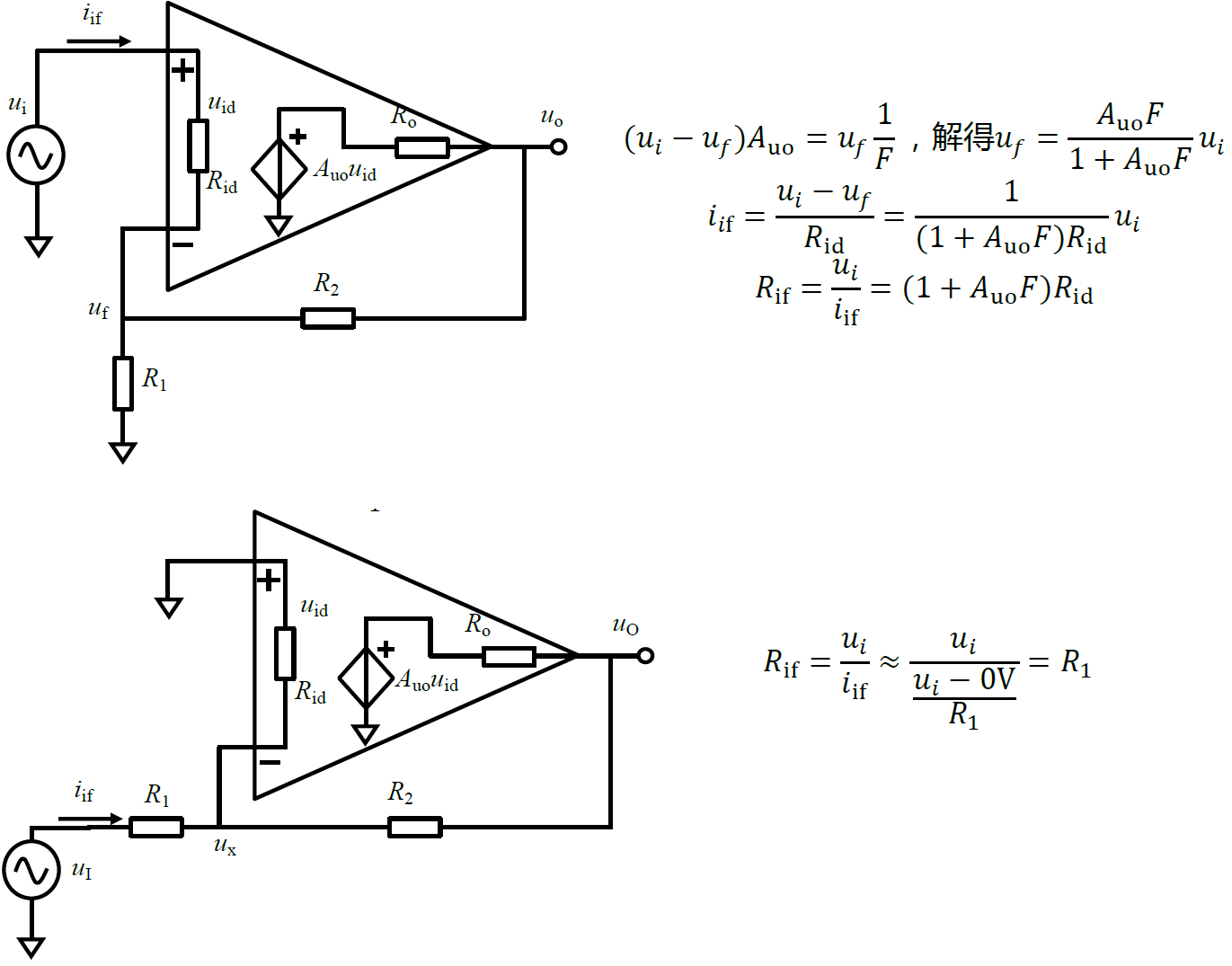

运放的输入阻抗

运放的输入阻抗跟结构有关,但是运放内部的阻抗很高,接近几百MΩ。如下图所示。

信号从正向端进入,使用正向放大电路,输入阻抗很高;信号从反相端进入,使用反向放大电路,输入阻抗很低。

运放的输出阻抗

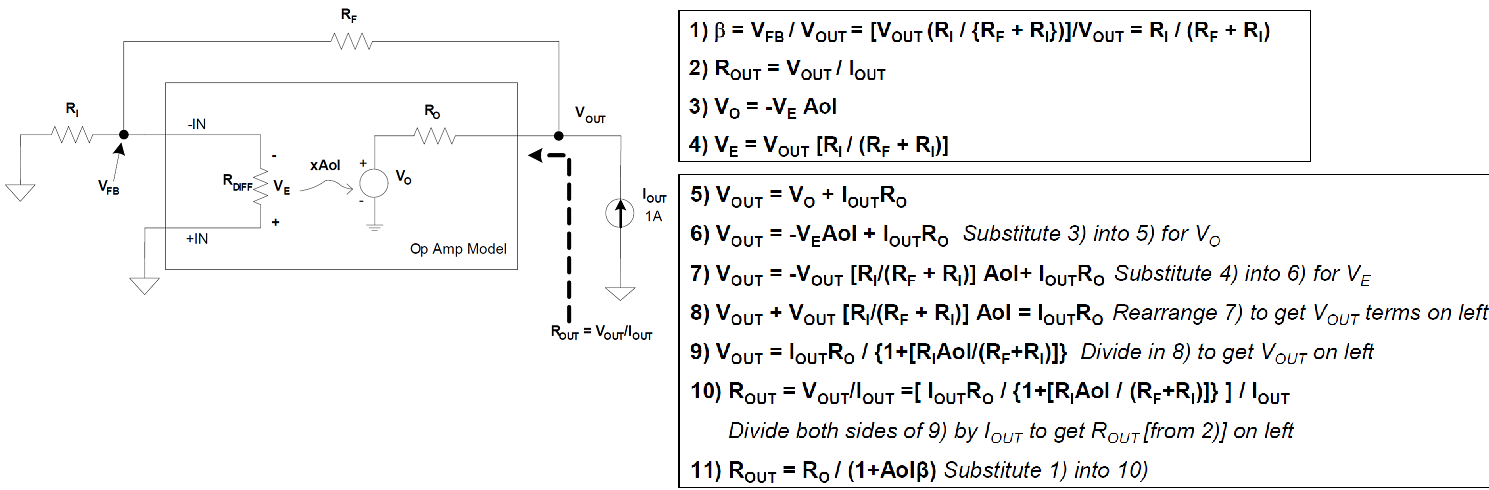

运放的开环输出阻抗固定为Ro,闭环输出阻抗与环路增益相关。如下图所示。

闭环输出阻抗Rout为开环输出阻抗的1/(1+Aolβ)倍,可知,当Aolβ为0(BODE图上为-∞)时,Rout≈Ro。

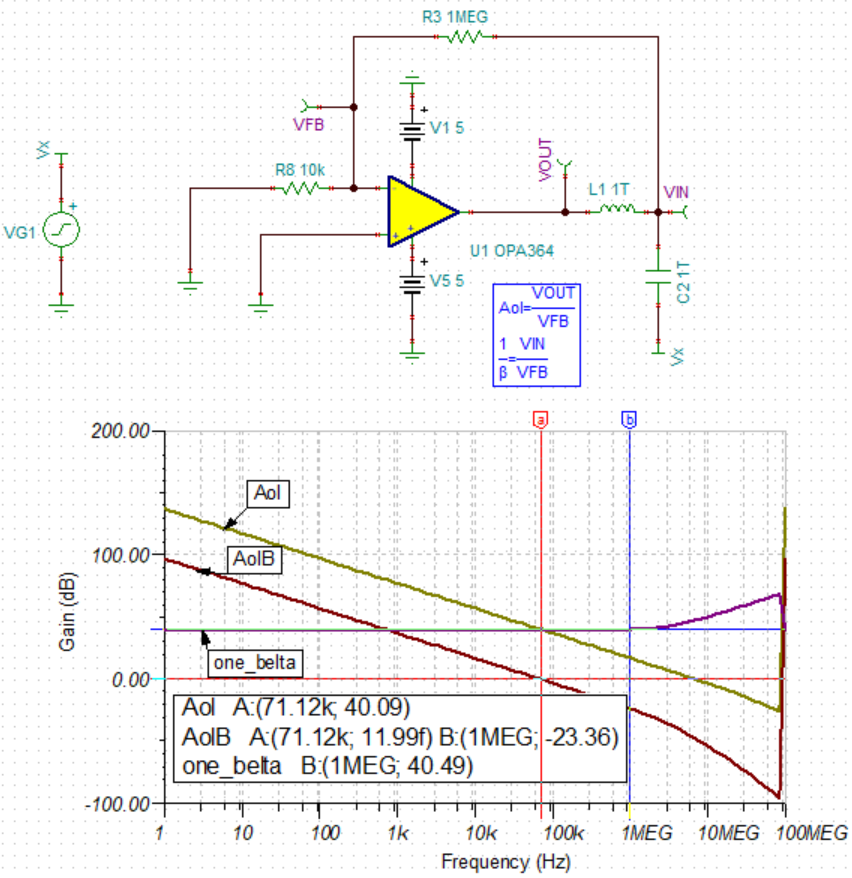

同样以OPA364为例子,仿真其环路增益Aolβ。如下图所示。

选择1/β=100=40dB,则Aol=40dB地方为Aolβ=0dB点,此时Rout=0.5Ro。在71.12kHz处,Aolβ=0dB=1,则Rout=Ro/2,闭环增益Acl=;在1MHz处,Aolβ=-23.36dB=0.06,则Rout=Ro/1.06。

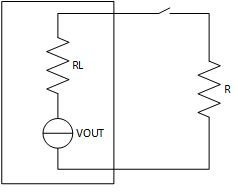

将整个系统等效为输出电压+内阻Rout,然后外接负载,测量负载电压。如下图所示。

分别使用71.12kHz和1MHz信号源,通过正向放大电路,输入为幅度为10mV的sin信号(有效电压为10mv/2^0.5=7.07mV)仿真,如下图(1MHz)所示。

1MHz时,开关打开时为50.29mV(无直流的交流电压值),闭合时为45.7mV。则Ro=1k X1.06 X(50.29/45.7-1)=106.5Ω。

71.12kHz时,开关打开时为511.05mV(无直流的交流电压值),闭合时为484.45mV。则Ro=1k X 2X(511.05/484.45-1)=109.8Ω。

两种结果近似相等,将等效电路图中的R4(160Ω)替换为109.8Ω或106.5Ω即可完美模拟处运放。

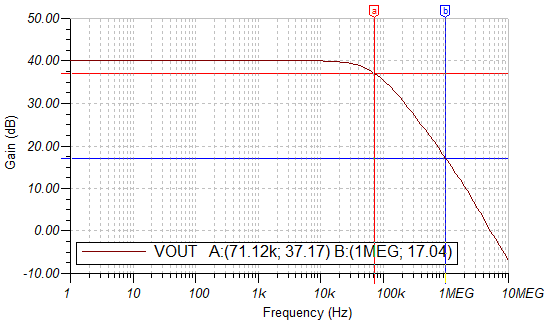

观察1MHz和71.12KHz时的闭环增益,如下图所示。

Acl(1MHz)=17.04dB=7.112,Acl(71.12kHz)=37.17dB=72.2,则对应的有效值分别为50.28mV和510.454V,可见与万用表测量的结果一致。