AI摘要:晶振是一种石英晶体振荡器,其名词解释包括公称频率及容许误差、基本波振荡及倍频振荡模态、负载电容、频率对温度稳定性、温度范围、等效串联阻抗、动态电容及动态电感、静态电容、驱动功率、电气品质因子、牵引率及敏感度、老化和储存温度范围、负性阻抗等。这些参数影响晶振的频率稳定性、温度特性、负载电容变化敏感度、老化率和储存条件等,对电路设计和应用至关重要。

Powered by AISummary.

晶振名词解释

晶振简单说明1

公称频率及容许误差(NominalFrequencyandTolerance)

在正确的振荡线路匹配下,从振荡线路输出的频率,称之为“公称频率(nominalfrequency)”。频率单位为MHz或KHz。

实际的批量生产及振荡线路应用上,产品在室温环境(25°)中都会有一些相对于中心频率的频率散布误差。这类型的频率容许误差的最大散布值,一般是以ppm(partspermillion)或%(percent)来表示。

频偏误差的计算公式如下:

频偏误差=(量测频率值–中心频率值)/中心频率值x1 000 000。(得出的单位为ppm)。

例如FC-12M的32。768kHz晶振,误差为20ppm,则说明最差情况下误差频率为32。768kHz*20/1000000=0。65536Hz。

1天需要振荡24x60x60x32768次,如果出现偏差则1天多振荡24x60x60x0。65536次,则是多了1。728s。

也可以这样计算:24x60x60x20ppm=1。728s。

基本波振荡及倍频振荡模态(FundamentalandOvertoneVibrationsMode)

在AT切割角度的石英晶体共振子主要是以厚度剪切振荡模态存在。石英晶体在共振时,除了基本波振荡之外,高阶的倍频共振也与基本波振荡同时存在于石英晶体的电极区域之间。但是,由于压电材料的电极是电气相位相反的振动环境,所以,祇有奇数倍(oddnumber)的高频倍频可以发生,偶数倍(evennumber)的倍频共振在石英晶体共振子是不会存在的。

负载电容(LoadCapacitance,CL)

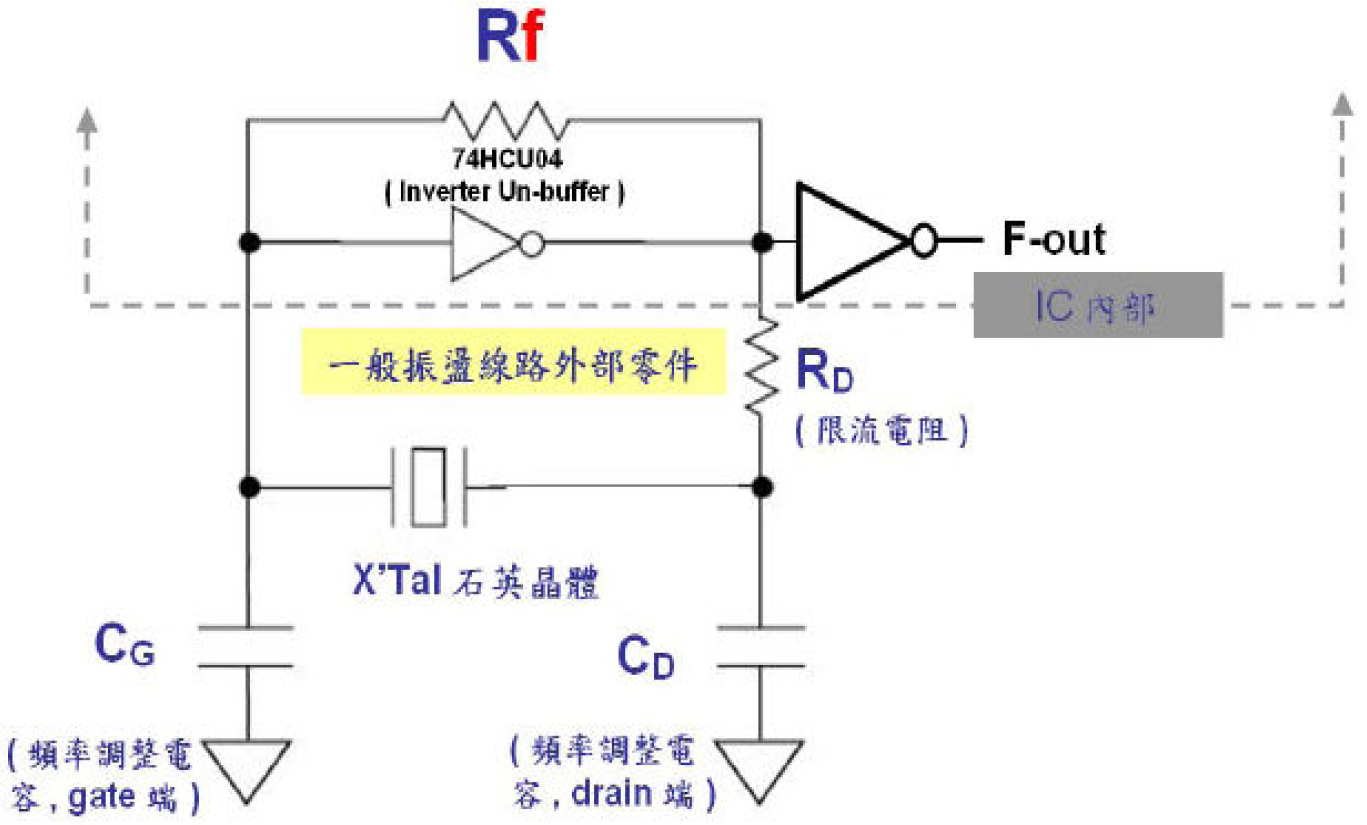

振荡线路上的”负载电容(loadcapacitance)”定义为:从石英晶体共振子的两个端子看向振荡线路所遭遇到的所有电容值。负载电容在线路上可以与石英晶体共振子以并联(parallel)或以串联(series)的方示连接。以并联方式连接的振荡线路中,负载电容(CL)的大小会影响公称频率的特性。这种负载电容并联线路的共振频率以fL表示。

频率对温度稳定性(Frequency-TemperatureStability)

石英频率因温度变化而改变,这是因起于石英材料在各个坐标轴向的热膨胀系数不同,当温度变化时,各轴向晶格距产生些许变化。当引用不同的切割角度时,不同振荡模态的之变化也会不同。

以AT切割角度的厚度剪切振荡模态的设计,一般是采用摄氏25度作为参考温度点的频率来定义在工作环境温度范围内的频率变动的稳定性。在定义这项频率对温度稳定性参数的同时,也应该一同规范出相对应的工作环境

温度范围(OperationTemperatureRange)

石英频率组件频率对温度稳定性的特性,亦如同公称频率误差一样,是以ppm或是以%为计量单位。组件的频率温度特性曲线与石英的切割角度,振荡模态,表面处理及外型尺寸都有很大的关系。除此之外,振荡线路上的负载电容(CL),驱动功率(drivelevel)的特性,也会影响到振荡线路输出频率对温度变化的稳定性。

等效串联阻抗(EquivalentSeriesResistance,ESR)

当石英晶体串联振荡在fs时,C1及L1是相反相位而互相抵消,整个共振子的动态支臂(motionalarm)的导纳(admittance)是接近最小阻抗值R1。这时候整个石英晶体共振子的表现仅是一个电阻性的组件。电阻值R1是整个组件的机械性能量损耗。其中包含了石英材料,接着材料及封装材料上所有的能量损耗。

动态电容(MotionalCapacitanceC1)及动态电感(MotionalInductanceL1)

在公式一中,动态电容C1及动态电感L1与串联偕振频率,fs,是相互关联的。

在实际的量测系统中,我们只能量测到动态电容C1及串联协振频率fs。动态电感L1是由公式(4)计算得到。

静态电容(StaticCapacitanceorShuntCapacitance,Co)

静态电容,Co,主要来自由以石英芯片为介电材料与两个电极所形成的电容为主;另外一小部份的静态电容来自连接石英芯片与接线的导电接着材料之间的电容和封装外壳的电容。

静态电容是在远低于振荡频率的范围量测出来的,以避免在受到振荡频率附近的动态电容影响。公式(5)是静态电容的数学表示式。

驱动功率(DriveLevel)

石英晶体的驱动功率是指石英晶体共振子的消耗功率。一般是以微瓦(microwatt)表示。振荡线路的设计上必须提供适当的功率让石英晶体共振子开始起振并维持振荡。石英晶体的振荡是属于物理上的高频机械振动,振荡时的电气阻抗值约在10-100奥姆以下(依频率范围及尺寸大小有差异)。振荡线路若提供过高的驱动功率,会使石英晶体的非线性特性变化及石英/电极/接着材料的接口恶化,进而造成振荡频率FL及等效阻抗R1的过度变化。石英晶体在长时期的过高驱动功率下工作,会有不稳定的现象。随着各类应用面的低消耗功率需求及产品小形化趋势,加上近几年石英产品的技术大幅提升,石英晶体共振子的电气阻抗值整体都下降而且稳定。振荡线路的设计不需要,也不应该提供过高的驱动能量在石英晶体共振子上面。对于绝大部份的应用面而言,振荡线路提供10~100微瓦(microwatt)的最大功率(视石英共振子的尺寸及频率而定)给石英共振子已足够了。

驱动功率是指石英晶体单元的消耗功率,其单位是微瓦(μW),可透过量测流经石英晶体的电流,再换算求出它所消耗的功率。功率量测值应该要小于个别晶体组件在规格上所定义的最大值,其计算公式为:P(uW)=I^2xRe

一个振荡线路在设计上必须提供适当的功率,以让石英晶体单元开始起振并维持振荡。此功率应该越小越好,除了能更为省电外,也和线路的安定性及石英晶体的寿命有关。振荡线路若提供过高的驱动功率,也会使石英晶体的非线性特性发生变化,以及造成石英/电极/接着材料的接口恶化,进而造成振荡频率和等效阻抗的过度变化。当石英晶体长时间在过高的驱动功率下工作,会出现不稳定的现象。以32kHz的石英晶体单元來說,当驱动功率过大时,有可能导致内部音叉型晶体的断裂;对于MHz等级的AT型晶体來說,则可能产生跳频现象,并影响石英晶体的寿命及可靠度。

电气品质因子(QualityFactor,Q)

对于石英晶体共振子,电气质量因子Q是很重要的一个特性。石英晶体的共振子的质量因子可以达到数佰万以上。

牵引率(Pullability)及敏感度(TrimSensitivity)

石英晶体共振子应用在并联振荡线路上,振荡频率与负载电容CL有很大的关系。是以并联振荡线路上FL频率对负载电容CL的变化曲线。

频率的“牵引率”指的是负载电容CL1的频率FL1到负载电容CL2的频率FL2的频率变化。可以是FL1(CL=24pF)与FL2(CL=10pF)的频率变化值。在这个例子中的频率牵引率是220ppm。若我们将CL1与CL2的负载电容值趋近极小化(曲线作数学上的微分),就会得到曲线的切线值。这个切线值就是用某一个负载电容的敏感度(trimsensitivity)。

CL=24pF时的频率敏感度是10ppm/pF,及CL=10pF时的频率敏感度是20ppm/pF。在并联线路中,负载电容越小,频率对负载电容变化的敏感度越高。相反的,负载电容越大,频率对负载电容变化的敏感度越低。这就是石英晶体共振子用于VCXO线路上时,线路设计上会选用较小负载电容。反之,在要求较准确的频率信号时,线路设计上会选用较高的负载电容。

老化(AGING)

“老化”顾名思意就是指在某一段特定时间范围内,石英晶体共振子随时间的频率变化,以百万分之一(partspermillion,ppm)为表示的单位。老化在频率与时间上的特性曲线,一般是呈现指数(exponential)型态的变化。频率老化变动最大的期间是在石英频率组件制成后的第一个月。之后,频率的变化就随时间逐渐减少。频率的老化特性有好几个主要的因素影响。比如说,封装的方法,材料的种类,制程温度,制程管控,热处理过程及产品的尺寸和频率高低。在规格上大多都要定义出短期(1-3个月)或长期(1-10年)的频率老化需求。

储存温度范围(STORAGETEMPERATURERANGE)

除了在前面的工作环境温度范围之外,另一项与温度有关的特性是”储存温度范围(StorageTemperatureRange)”。这个参数指的是产品在静态状况下可以储存的最高与最低温度范围。在这个温度范围内,产品必需保证在长时期的储存后,还是可以在工作温度范围内正常的工作并符合规格。这项特性与石英晶体共振子的组件设计及制程设计有很大关系,要小心的定义。

负性阻抗(NegativeResistance,-R)

负性阻抗是指从石英晶体共振子的二个端子往振荡线路看过去,所遭遇到振荡线路在振荡频率时的阻抗特性值。振荡线路上必需提供足够的放大增益值来补偿石英晶体共振子在共振时的机械能损失。负性阻抗并不是石英振荡子的产品参数,却是振荡线路的一项重要特性参数。从共振子的角度而言,就是在振荡线路的”负性阻抗”。

负性阻抗并非真实发生的阻抗值,而是在石英晶体旁边外加一个电阻(RS),去仿真石英晶体内部的ESR被加大时,整个振荡线路是否仍能被正常起振。

负性阻抗的量测值越大越好,这表示此一振荡线路越容易被起振;负性阻抗值不足时,则表示此一振荡线路会有起振过慢的现象,甚至可能导致不起振的狀况发生。负性阻抗的判断基本值是石英晶体最大ESR值的3~5倍。