AI摘要:本文以AD8603为例,详细解析了运算放大器的参数,包括输入特性(输入失调电压Vos、输入偏置电流Ib、输入失调电流Ios、输入电容/输入电阻Cin/Rin、输入电压范围Vin)、大信号电压增益Aov、共模抑制比CMRR、输出特性(输出电压Vout、短路电流Is、闭环输出阻抗Rout)、电源(电源抑制比PSRR、电源电流Iq)、动态性能(压摆率SR、全功率带宽FPBW、建立时间ts、增益带宽积GBW、开环增益Aol、增益裕量Am、相位裕量Φm)、噪声性能(峰峰值噪声、电压噪声密度、电流噪声密度、通道隔离)以及结温。通过这些参数的分析,可以更好地理解和应用运算放大器。

Powered by AISummary.

运算放大器——参数说明

以AD8603为例,进行图、表参数解析

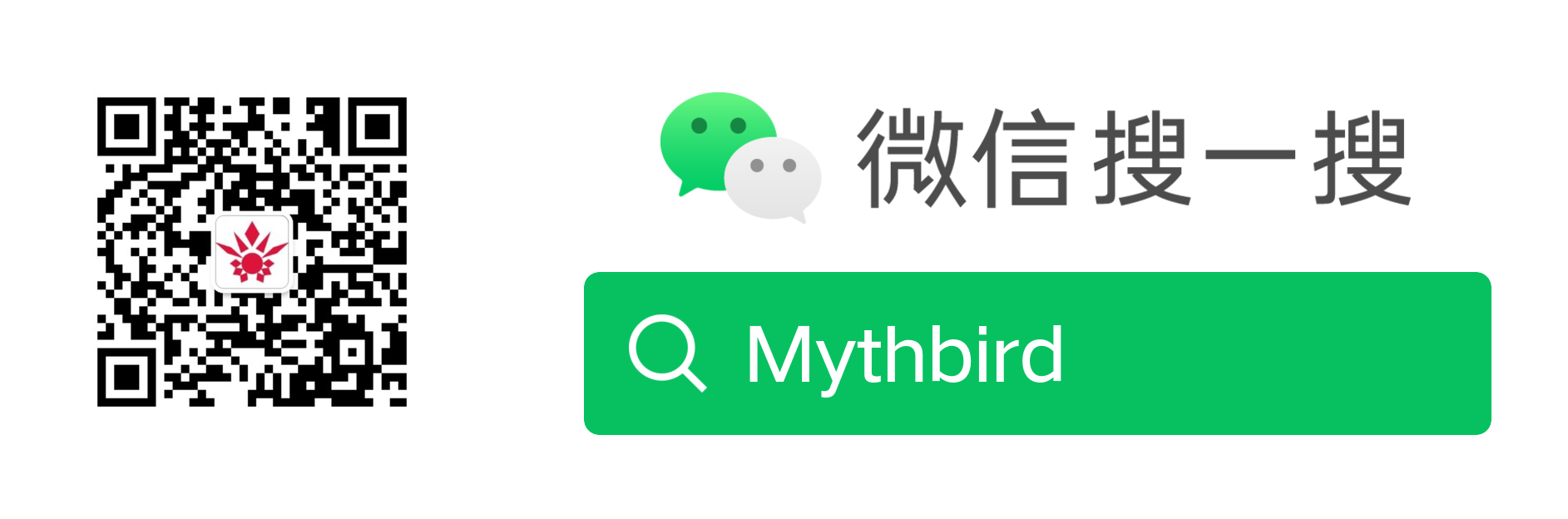

AD8603的参数表如下图所示。

输入特性

输入失调电压Vos

源于运放差分输入级两个管子不匹配所致,其结果是差分输入两端电压相同时,输出不为0。输入失调电压有温漂效应,故总的Vos需要加上温漂的结果。

Vos可看作一个共模输入电压,或者正端/负端的电压源,其为直流电压源。

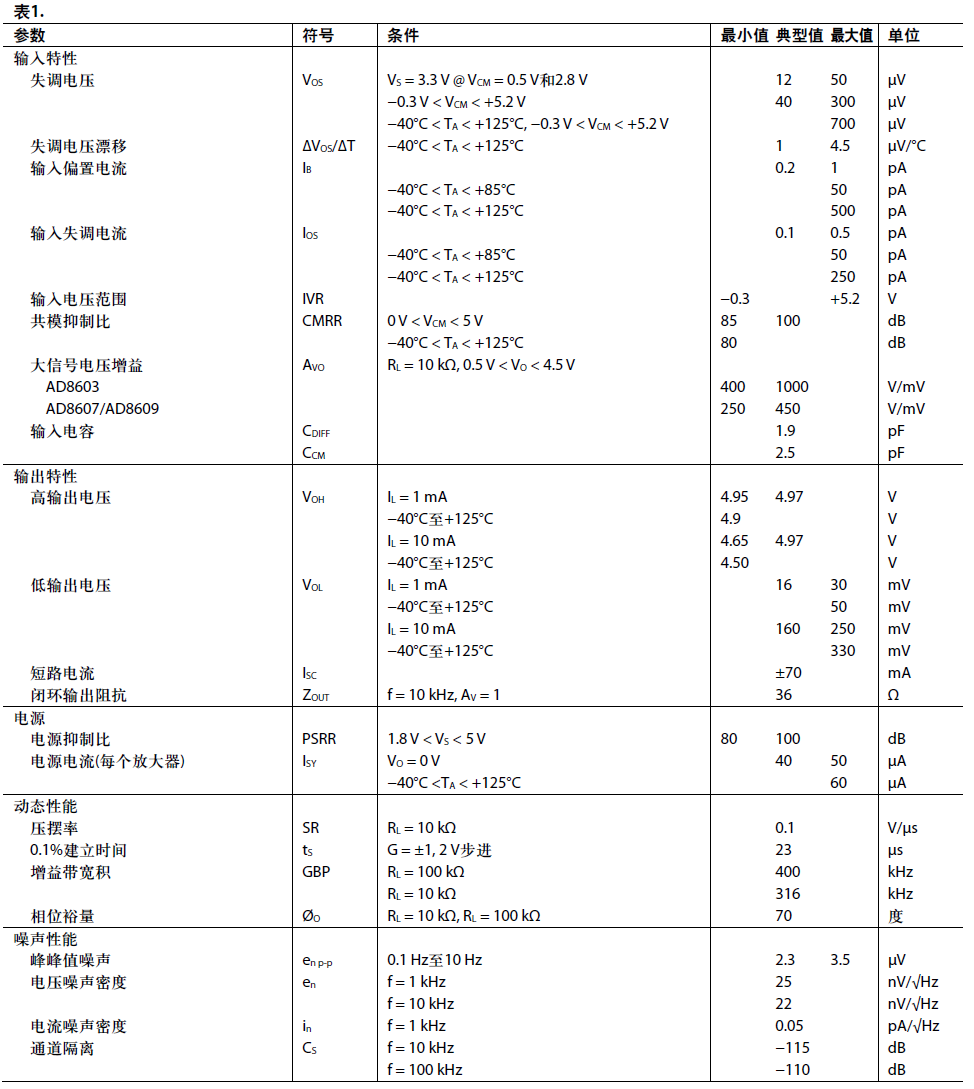

AD8603的输入失调电压如图所示,根据6σ原则,90%分布在±50uV,60%在±12uV,温漂最大在1uV/℃左右。在共模电压为4.0V时出现交越失真,输入失调电压出现翻转,会导致信号微小畸变。

输入失调电压的最终值为相应共模电压下的值+温漂效应产生的变化值。

常见类型的运放失调电压范围如下图所示。

输入偏置电流Ib

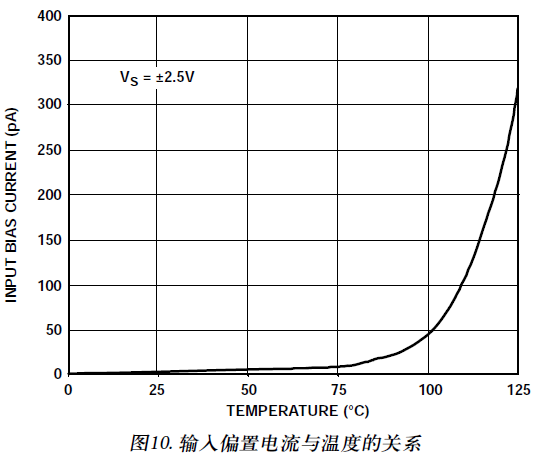

源于两个输入级有漏电流效应。两个漏电流的平均值就是输入偏置电流。其也有温漂效应。

当然为了正常工作,运放的输入电路都要求一定量的偏置电流,即要求正端到负端必须有电流流过,整体上形成电流环路。

输入偏置电流流过外部电阻网络,产生失调电压,导致输入有误差。

输入失调电流Ios

同上。两个漏电流的差值为输入失调电流,其也有温漂效应。

对于三极管的输入级,由于基级需要提供偏压或者需要驱动电流,而管子不完全匹配,导致电流不一样。

对于FET的输入级,由于是电压驱动,栅级驱动电流很小,但是输入级一般有ESD保护,而ESD有漏电流,同样ESD的不一致会导致电流不一样。为了保证两边的ESD漏电流相当,两端输入电压的共模电压应该相等,一般设置为电源电压的中心电平(但是要考虑共模电压的范围要求),可以通过电阻拉到中心电平,也可以通过上电阻和下电阻分压拉到中心电平,或者上电阻拉到正电源、下电阻拉到负电源。

对于CMOS的输入级,输入偏置电流和输入失调电流很小。

这里要解析下,运放电路中的补偿电阻的含义,在模电中只提到为了“保证集成运放输入级差分放大电路的对称性;其值为输入接地时反相输入端总等效电阻,即各支路电阻的并联”。可参考论文1

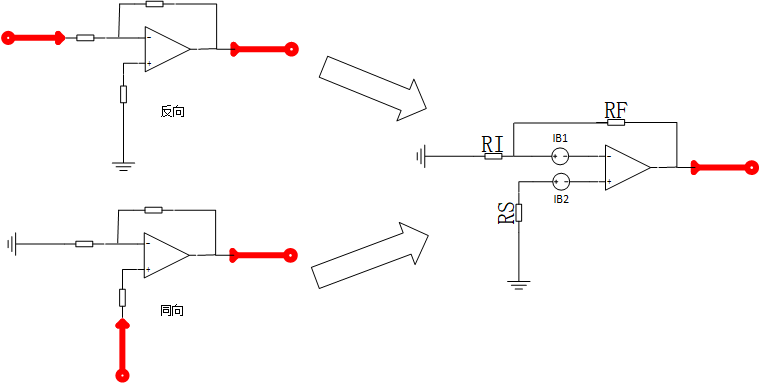

这里,分析下反向放大和同向放大,对于输入偏置电流的影响分析,可以先将输入去掉(接地),可见反向与同向都是一样的结果,如上图所示。

现在同样,将两个偏置电流分开分析,最终两个偏置电流对Vout的影响如下所示。若要偏置电流的影响为0,则RS为RF与RI的并联,推导如下所示。

输入电容/输入电阻Cin/Rin

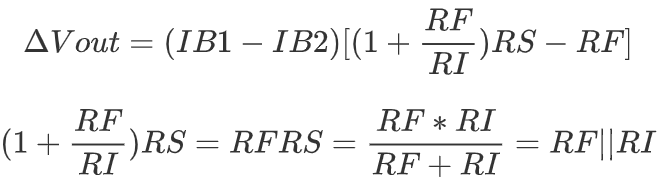

下面使用等效电路说明运放的输入电容和输入电阻概念。

- 输入失调电压:Vos

- 输入偏置电流:(Ib1+Ib2)/2

- 输入失调电流:Ib1-Ib2

- 输入差模电容:Cdiff

- 输入共模电容:Ccm

- 输入差模阻抗:Rdiff

- 输入共模阻抗:Rcm

对于BJT的运放,Rcm一般大于40MΩ,Rdiff一般大于200GΩ,JFET和CMOS的要大很多,故一般不考虑输入阻抗问题。

AD8603的输入差模电容为1.9pF,输入共模电容为2.5pF。

输入电压范围Vin

在IN+和IN-端加上的电压范围。根据输入电压是否可以达到电源电压分为轨至轨和非轨至轨输入。

JFET和BJT一般为非轨至轨输入。

输入电压范围受输入共模电压的限制。这里分两种情况,反向放大电路中,正向端接参考电源Vref,当Vref为0V时,则输入共模电压为0V,否则为Vref,此时就要判断共模电压为Vref是否在允许的范围内。同向放大电路中,共模输入电压则是输入信号电压,同样也要判断是否在允许范围内。

为什么会有这样的限制?是因为集成运放的输入端一般为BJT或者FET、CMOS对管构成,而由于偏置输入电流流过对管,产生压降,导致输入范围降低,这就是非轨至轨输入的原因,当然可以通过电荷泵或者采用NMOS与PMOS差分输入级并联的方式去抵消甚至提高输入电压范围,来形成轨至轨输入。电荷泵方式会有一定的噪声(以一定频率的电容充放电方式提高电压),后者由交越失真区域(Vos出现电平翻转),后者可以通过数字调零或者自调零技术实现极低的交越失真。

具体分析见TI Precision Labs2

AD8603为轨至轨输入,输入电压为(Vs-)-0.3~(Vs+)+0.2,Vs-=0,Vs+=5。

大信号电压增益Aov

相当于直流信号(或低频信号)的增益,等同于开环增益Aol。很少用。

1000V/mv=1000 000V/V=120dB

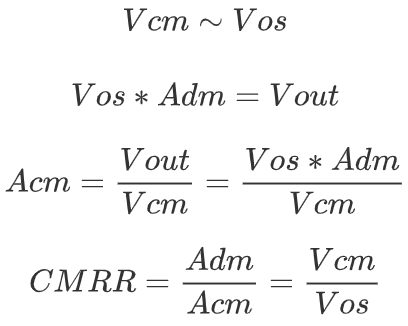

共模抑制比CMRR

差模增益/共模增益。

运放只所以会对共模信号能够进行放大主要来源于下面几个原因3:

运放差入输入级的不匹配。这又可分为以下的原因引起的不匹配:

- 源极或漏极电阻的不匹配,

- 信号源电阻

- 栅极-漏极之间的结电容

- 正向跨导的不匹配

- 栅极漏电流

- 拖尾电流源的输出阻抗

- 拖尾电流源的寄生电容会随频率的变化而变化

理论上共模增益为0,即共模电压被差分为0,输出电压为0。但是实际情况是共模电压会产生输入失调电压,该失调电压会被差分放大(以差分增益放大)到输出,导致输出不为0,该输出与共模电压的比值则为共模增益。用公式说明如下。

通过测量输入共模电压的变化ΔVcm与其导致的输入失调电压的变化ΔVos的比值可得CMRR=ΔVos/ΔVcm。

例如,CMRR=130dB@1kHz,若共模电压为5V,则对应失调电压为Vos=5V*10^(130dB/20)=1.58uV。

故要特别注意反向放大电路中加入的参考电压或者中心电平,同向放大电路中的输入电压,这两种电压形成的共模电压,其造成的失调电压是否会被放大畸变或者直接导致输入信号畸变。

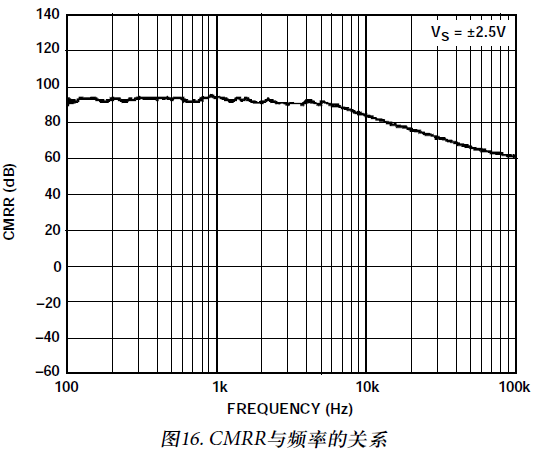

CMRR与频率成反比,频率越高CMRR越小。

AD8603的CMRR与频率的关系如下图所示。

输出特性

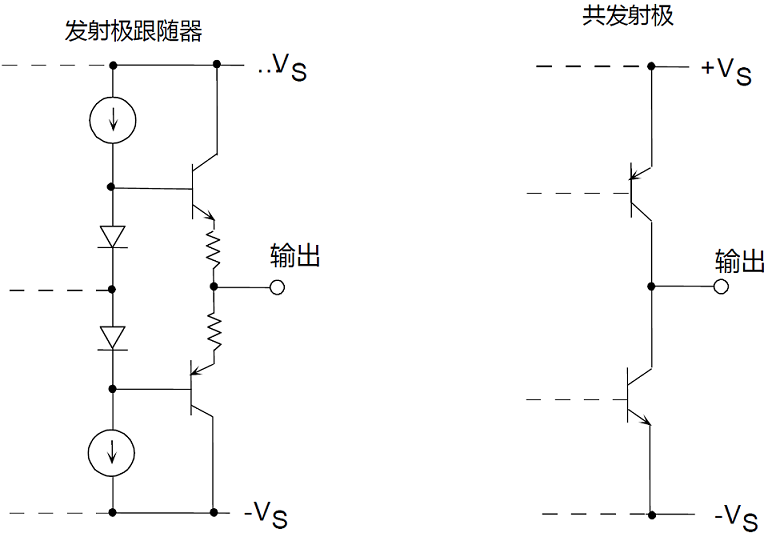

输出电压Vout

轨至轨输出指的是输出电压接近电源轨,而不会等于电源轨。对于BJT类型的运放,输出一般采用互补共射级输出,输出电压只能摆动到电源轨的晶体饱和电压Vce范围内(VCC-Vce)。对于FET型输出为推挽输出,由于FET上存在导通电阻Rds,输出电流在Rds上存在压降,导致始终不会达到电源轨。常用BJT的输出结构如下图所示。

左边结构适合高频,右边适合低电源电压。

另外由于导通电阻有正温度系数,导致温度越高电阻越大,输出电压越小。同样负载电流越大,输出电压也越小。

AD8603的输出电压与负载电流关系如下图所示。

由上图可知,负载电流越大,输出电压到电源轨的差越大,温度越高,摆幅越大(输出电压摆幅就是从电源轨到输出电压的变化)。

短路电流Is

短路电流用于表明输出级灌入电流的能力,反映了运放对负载的最大驱动能力。分为源电流和灌电流,前者为输出,后者为输入。灌电流为输出低电平时,可能来自外部的电流。

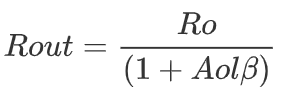

闭环输出阻抗Rout

Ro为运放的开环输出阻抗,Rout为运放的闭环输出阻抗。其中Ro为固有阻抗,两者的关系是:

其中Aol为开环增益,β为反馈增益。

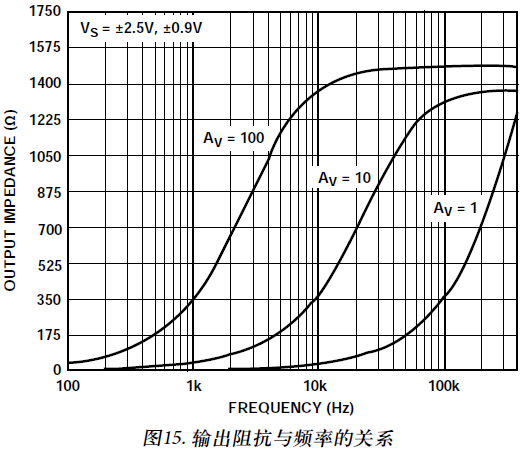

Aol与频率成反比,则Rout与频率成正比。即频率越高,闭环输出阻抗越大。

图中Av表示电压增益。可见频率越高闭环输出阻抗越高。

闭环输出阻抗可用于计算开环输出阻抗,当驱动容性负载时,开环输出阻抗Ro会与容性负载形成极点,可能导致系统不稳定,形成振荡。

电源

电源抑制比PSRR

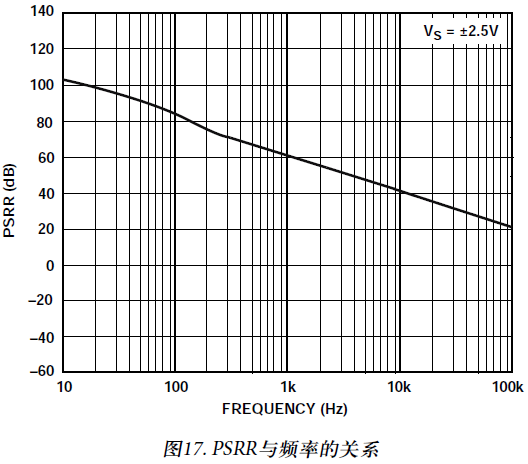

当运放的电源电压变化时,运放的输入失调电压Vos也会变化。两者的比值就是电源抑制比,PSRR=ΔVcc/ΔVos(与CMRR有相似之处)。同样造成了Vos的变化,必然会导致输出扰动。

PSRR和CMRR一样,都与频率相关,成反比关系。

AD8603的PSRR如下图所示。

电源的波动导致Vos变化,为了得到稳定的输出或者说减小噪声干扰,需要使用低噪声电源如LDO,避免使用DC/DC电源。如果系统中使用了多个运放,可以考虑在运放前加RC滤波电路(R值很小)或者Π型隔离滤波电路,防止器件间干扰。

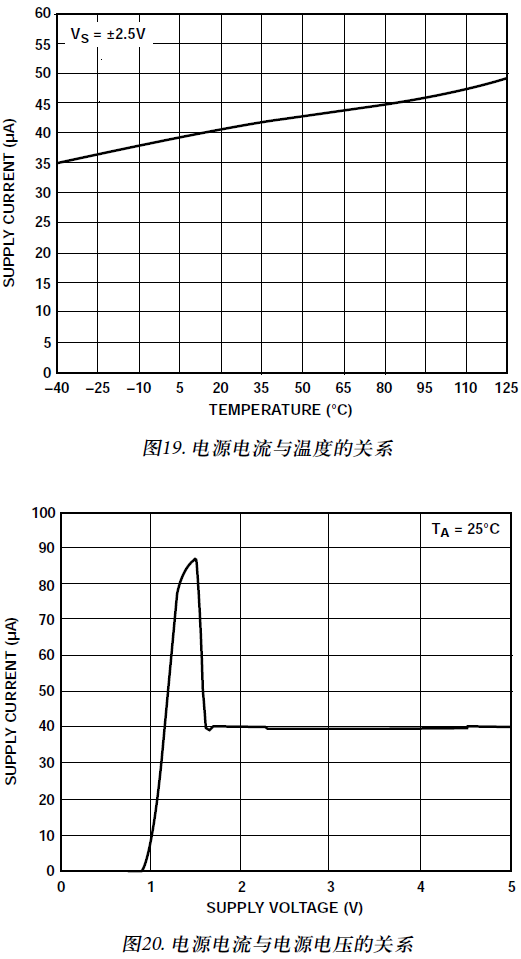

电源电流Iq

运放无负载情况下的静态功耗。

AD8603的工作电流与温度和供电电压有关,如下图所示。

动态性能

压摆率SR

输入端的阶跃变化导致的输出端电压变化的速率,为ΔV/Δt,单位一般为V/us。反映了大信号的输出能力,表示信号摆动速度的最大值。

压摆率主要由内部的补偿电容决定,该电容会形成密勒效应,导致电容变大,信号会经过充放电过程,从而影响输出信号。

为了保证输出信号与输入信号变化率一致,运放的压摆率必须大于等于输入信号的摆率。

全功率带宽FPBW

FPBW=SR/2ΠVp,Vp为输出满赋值。

已知SR和信号的输出电压幅值Vp,则可以得到信号的频率。

举例,输出为100kHz Vp=10V,则其SR=6.3V/us,可见运放必须支持SR≥6.3V/us。

压摆率反应的是阶跃信号的输出能力,而全功率带宽反应的是正弦输入信号(或者说周期信号)的输出能力。

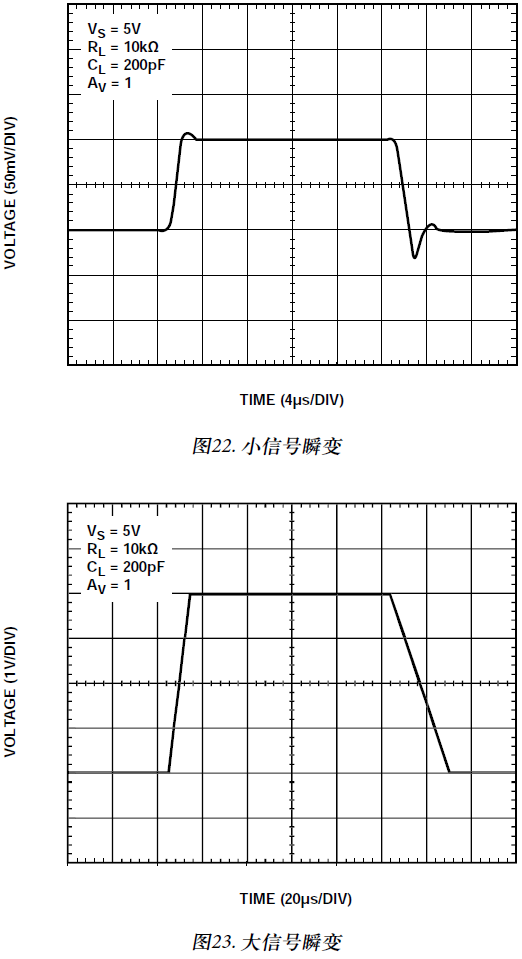

建立时间ts

建立时间就是阶跃响应的稳定时间。

后级电路对时间有要求的会受此影响,比如ADC,需要采样建立保持时间。

运放的建立时间与SR(大信号)和闭环增益Acl(小信号)有关。SR较大时,达到目标电压时间短。闭环增益Acl较大时,输出电压变化大,根据SR其达到目标电压时间变长。

AD8603大/小信号的建立时间如下图所示。

增益带宽积GBW

小信号在开环增益曲线中,单位增益Aol=0dB(1)时的带宽为fc,其GBW=fc*1=fc。

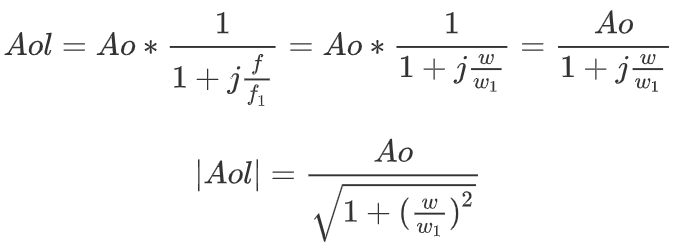

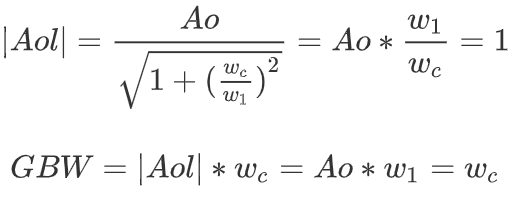

为什么GBW为常数?下面进行说明。

开环增益Aol在低频处有极点,曲线呈-20dB/Decade下降趋势,直到0dB位置。一般在高频处还有个极点。假设前者为w1,0dB处为wc。由于wc是在-20dB/Decade斜率曲线上,而曲线的弯折位置为w1。类比低通电路的电压增益,可知开环增益Aol可用如下方程式表示:

Ao为低频处(弯折前)的增益。

可知wc为:

而Ao>>1,故wc>>w1,wc/w1>>1。

在wc处,|Aol|和GBW分别为:

从而说明了GBW为常数,且就是单位增益的频率。

运放的GBW越高,所需要的电流也越大,而且MOSFET所需的电流比BJT的要大。

开环增益Aol

开环增益曲线与运放的稳定性有关,这个可以参考4

由于开环增益并非无穷大,故会导致闭环增益并非是电阻网络的比例值,存在一定误差。

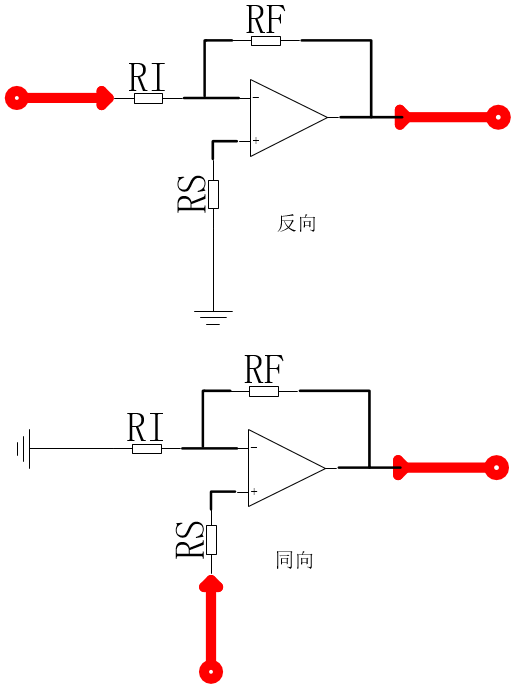

以反向和反向放大电路为例,如下图所示。

两者的闭环增益误差推导如下:

可见放大器的闭环增益误差百分比就是开环增益的倒数。

开环增益越大误差越小,故开环增益小的运放不适合高精度信号的放大。

增益裕量Am

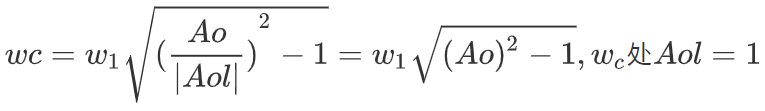

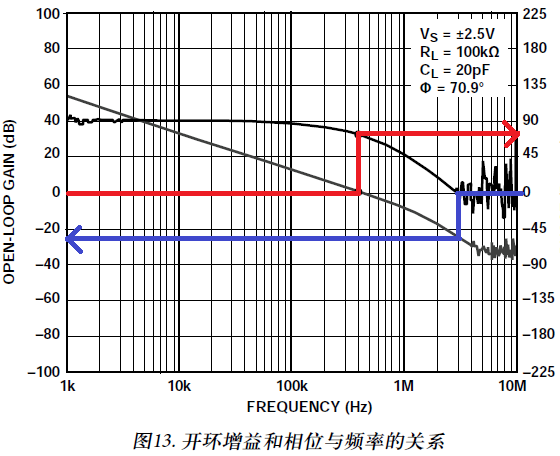

增益裕量定义为相位变化180°时的增益与单位增益(0dB)的差值,其实就是相位变化180°后的增益。

AD8603在0dB处频率为400kHz,在0°处频率为3MHz,增益为-30dB,可见增益裕量为0dB-(-30dB)=30dB。如蓝线所示。

相位裕量Φm

相位裕度定义为单位增益处的相位与相位从开始变化180°后的相位之间的差值。

AD8603的单位增益处频率为400kHz,该处相位从180°变为70°,相位从180°变化180°后为0°,故相位裕量为70°-0°=70°。如红线所示。

噪声性能

运放的噪声分析可以参见5

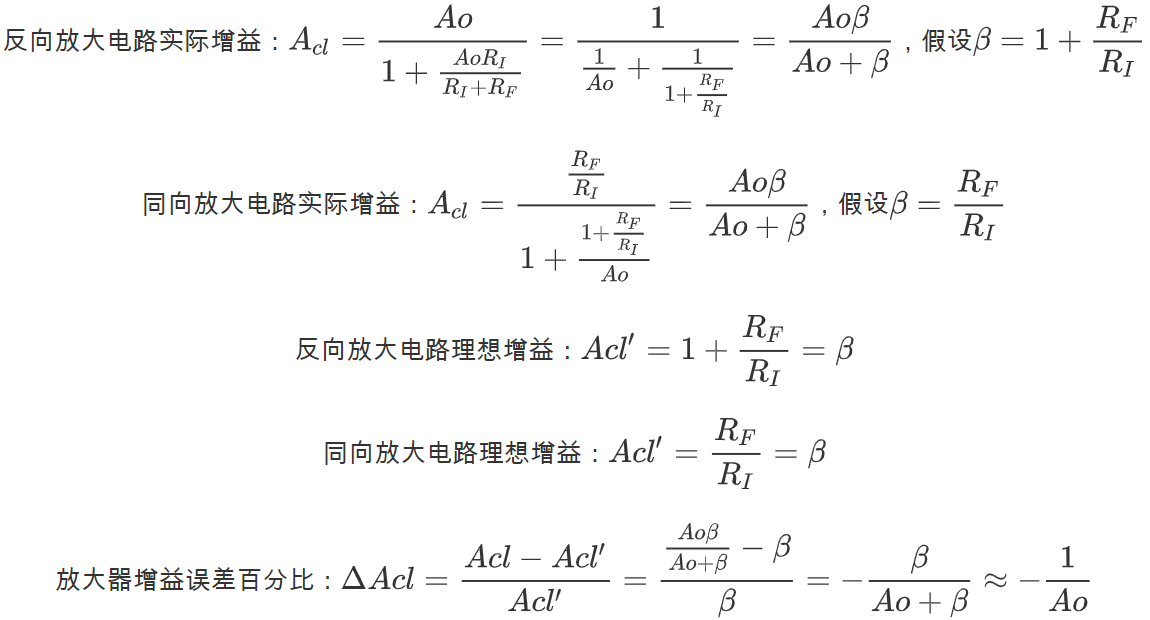

峰峰值噪声

峰峰值噪声主要在低频区域(0.1Hz~10Hz)即1/f噪声,体现出运放自身的最大噪声特性。

电压噪声密度

输出端的噪声除以放大器增益,就是输入端的噪声。

电压频谱密度Vn,单位是V/√Hz:其实噪声是个能量概念或者说功率概念,噪声的总功率(W)为在整个频域内分布的功率之和,所以噪声密度的单位是 W/Hz,但是平常习惯用电压电流表示信号,所以要把功率换算成电压,开平方后就成了V/√Hz6。

电流噪声密度

电流频谱密度In,单位是A/√Hz。

通道隔离

可能是多路运放,通道间的隔离程度。

结温

运放静态功耗和驱动负载产生的功耗,引起的温升。具体见7